## Don't keep your CPU waiting Speed reading for machines

z/OS Performance Education, Software, and Managed Service Providers

www.pivotor.com

#### Agenda

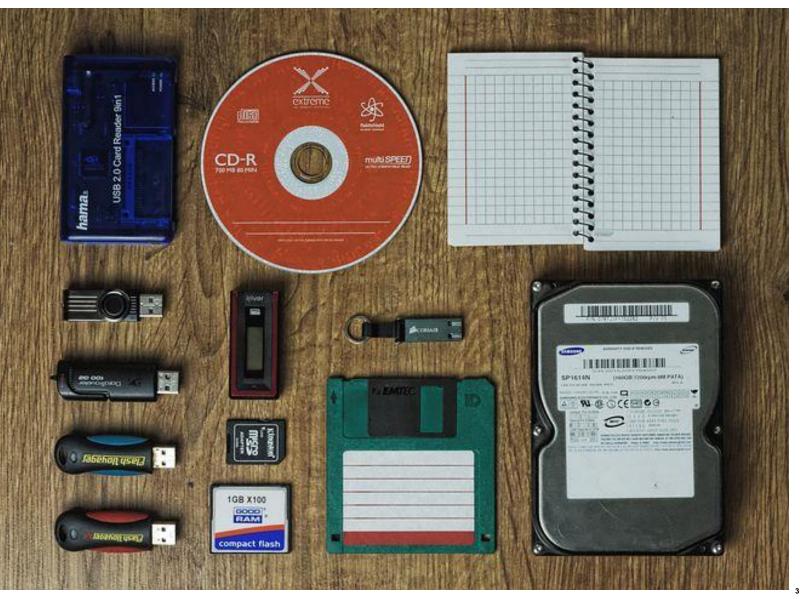

- Storage vs storage

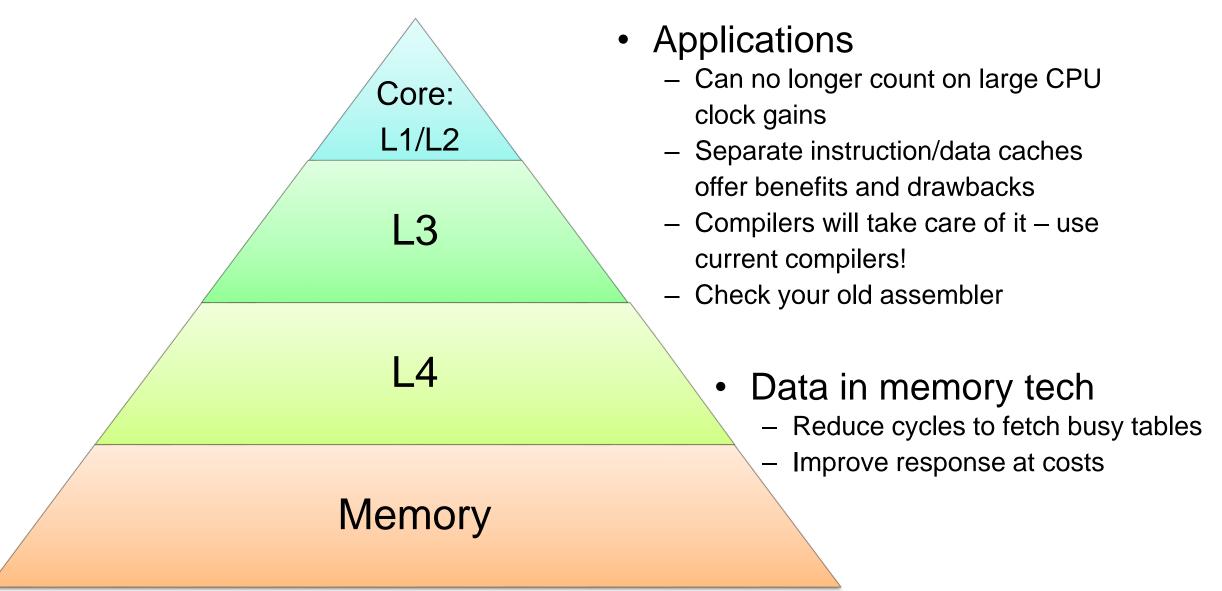

- CPU and processor caches

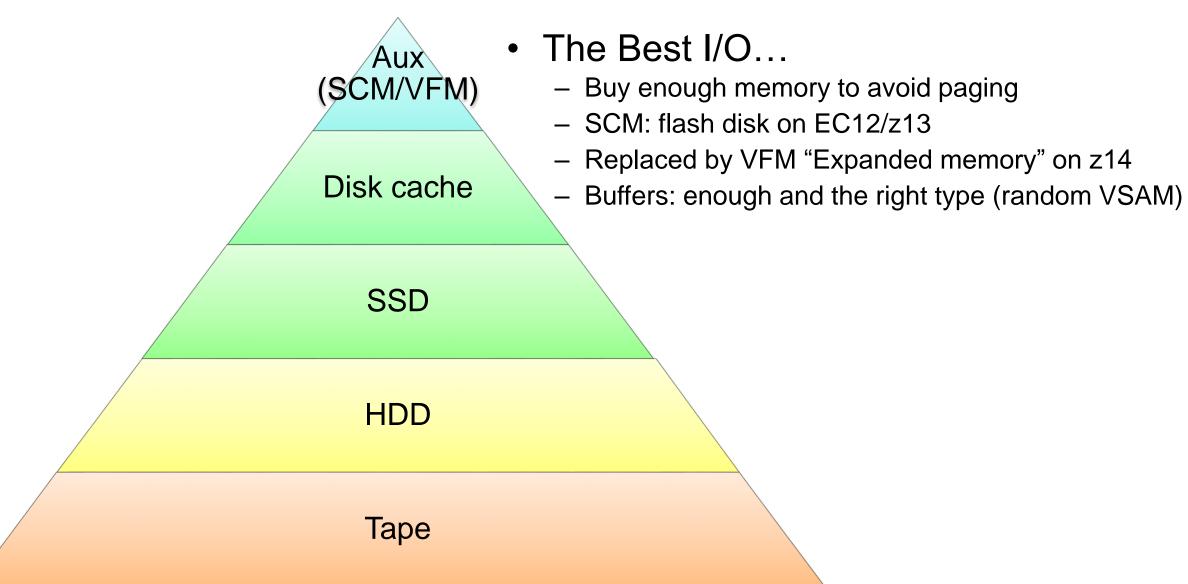

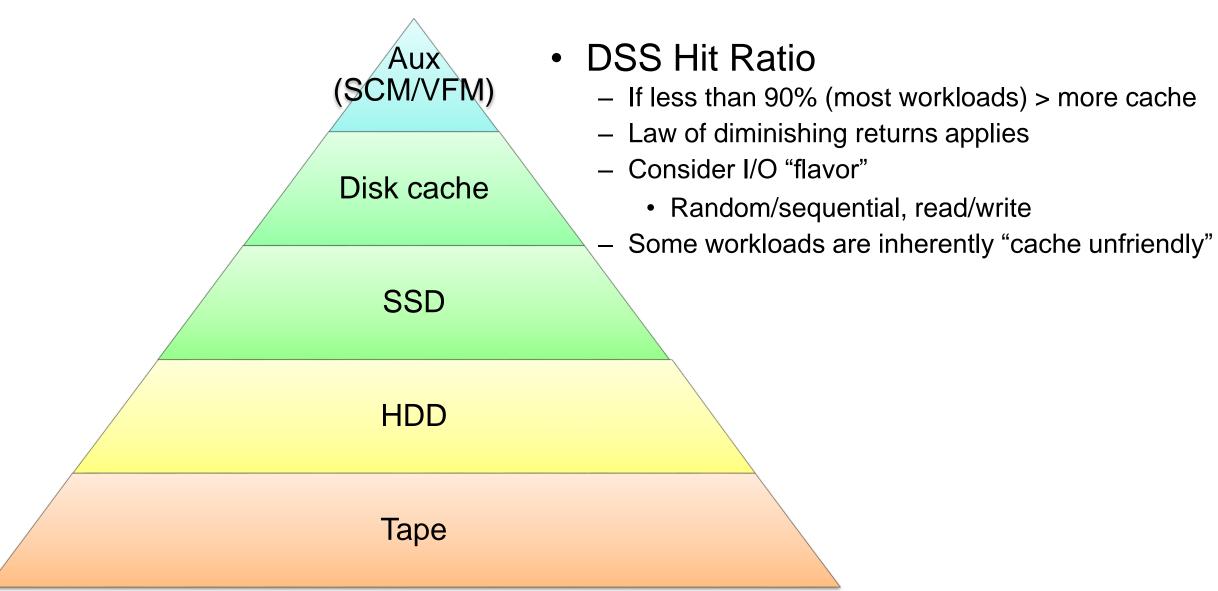

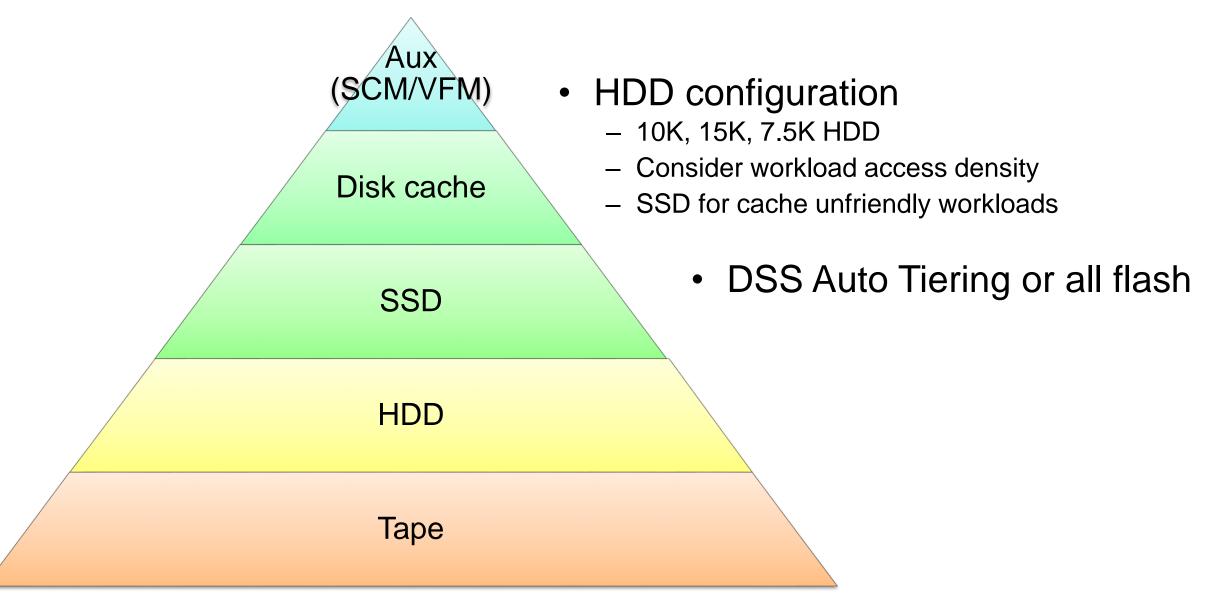

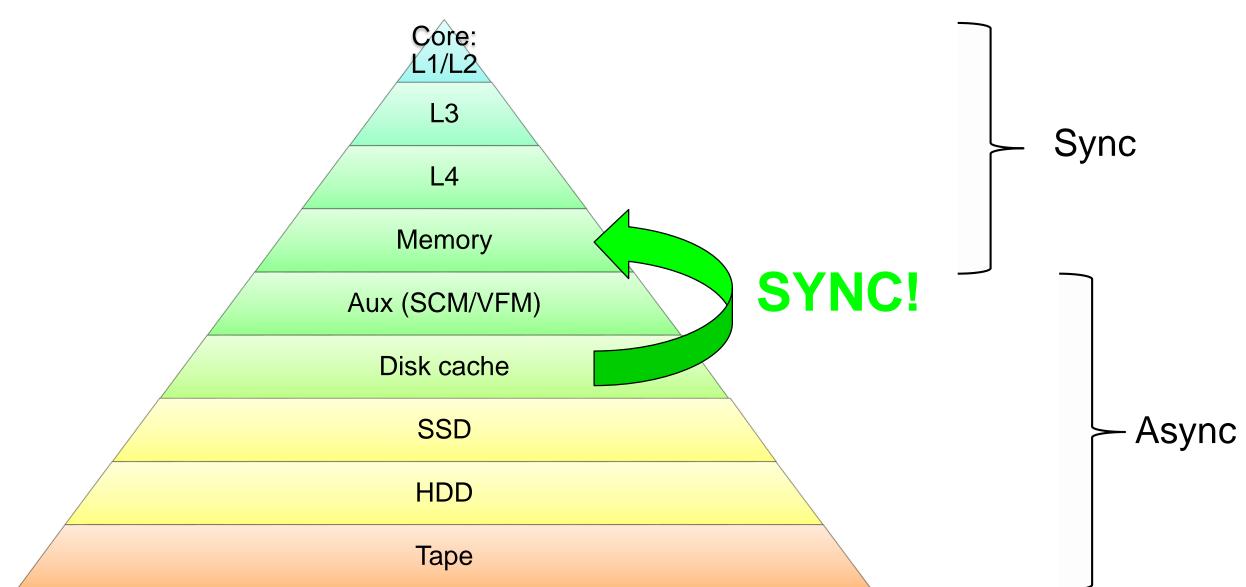

- Storage tiers

- Sync vs Async

- Basic cache principles

- Improving sync access

- Hiperdispatch and DAT

- Improving async access

- DSS stats

- RMF stats

- zHyperLink

## Storage vs Storage

#### All roads lead to the CPU

• z14: 5.2 GHz = .192 ns cycle time

4

## How far can I go in .192 ns?

- Speed of light = 300,000 km / sec

- = 30 cm / ns

- 30cm ~ 12 inches \* .192

- **= 2.3 inches**

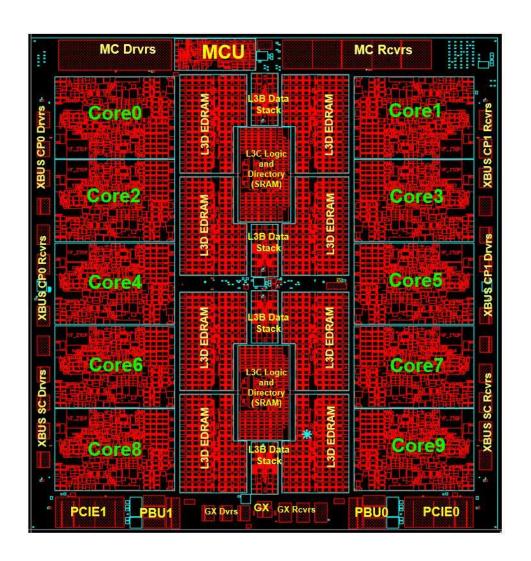

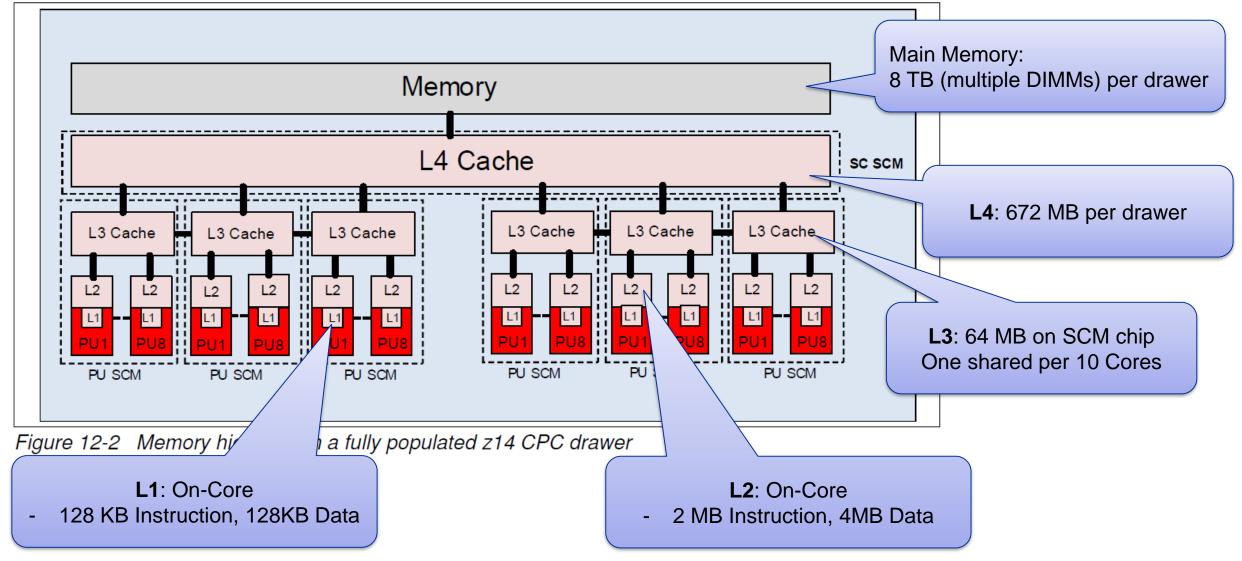

#### z14 PU Chip

- 14 nm technology

- 6.14 billion transistors

- 23.2 km or 14.4 miles of wire

- Up to 10 cores

- L3 cache on chip

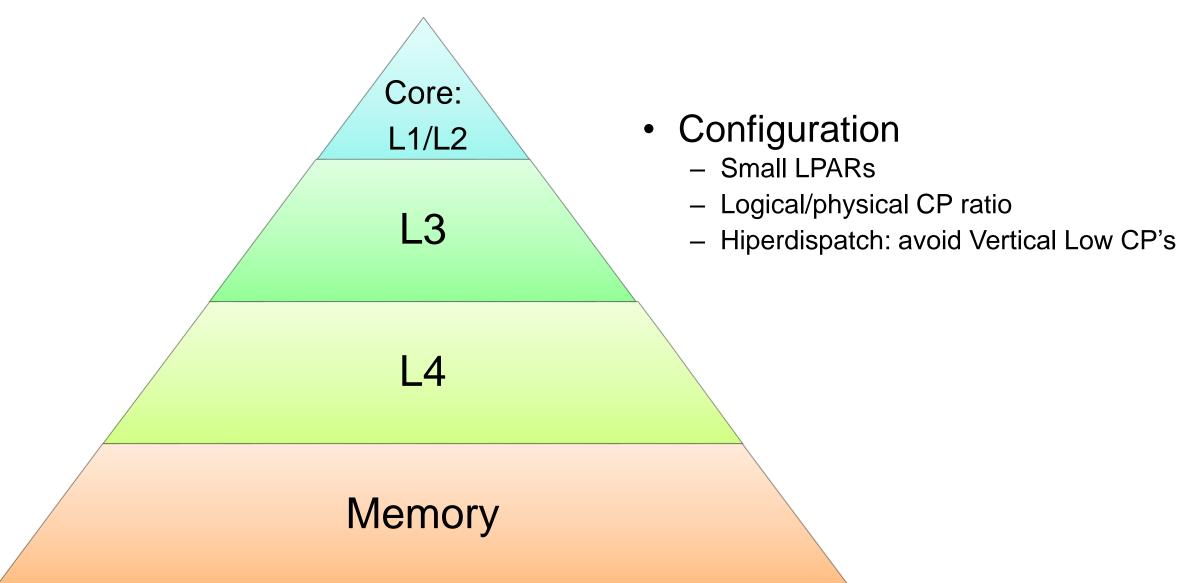

#### **Processor Caches**

7

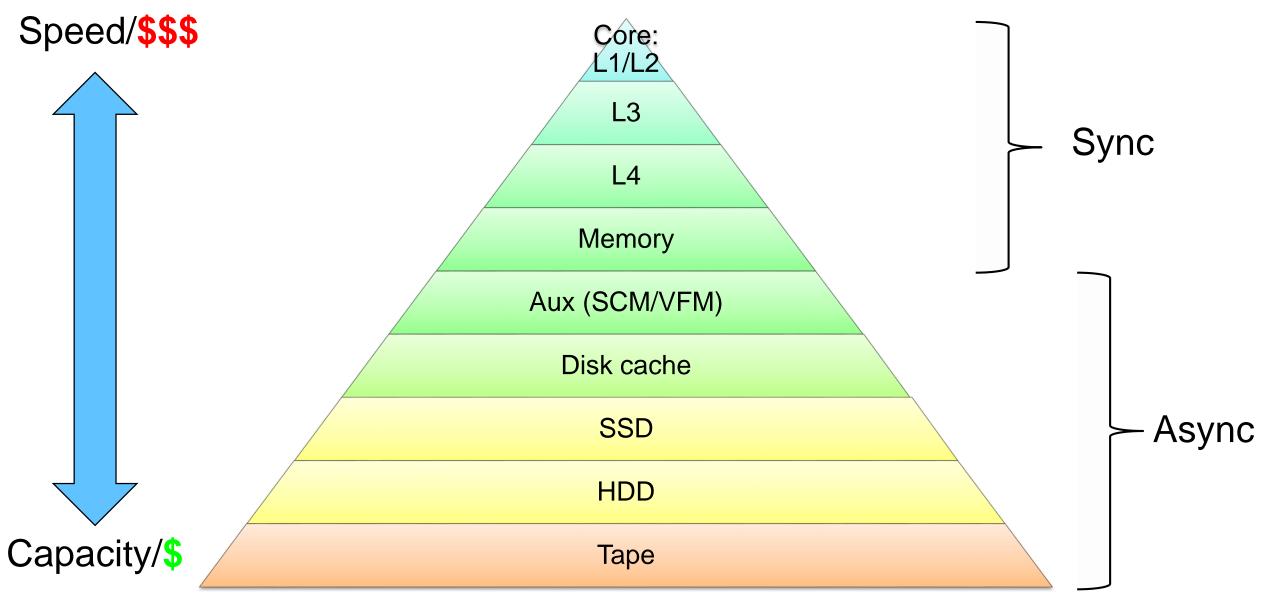

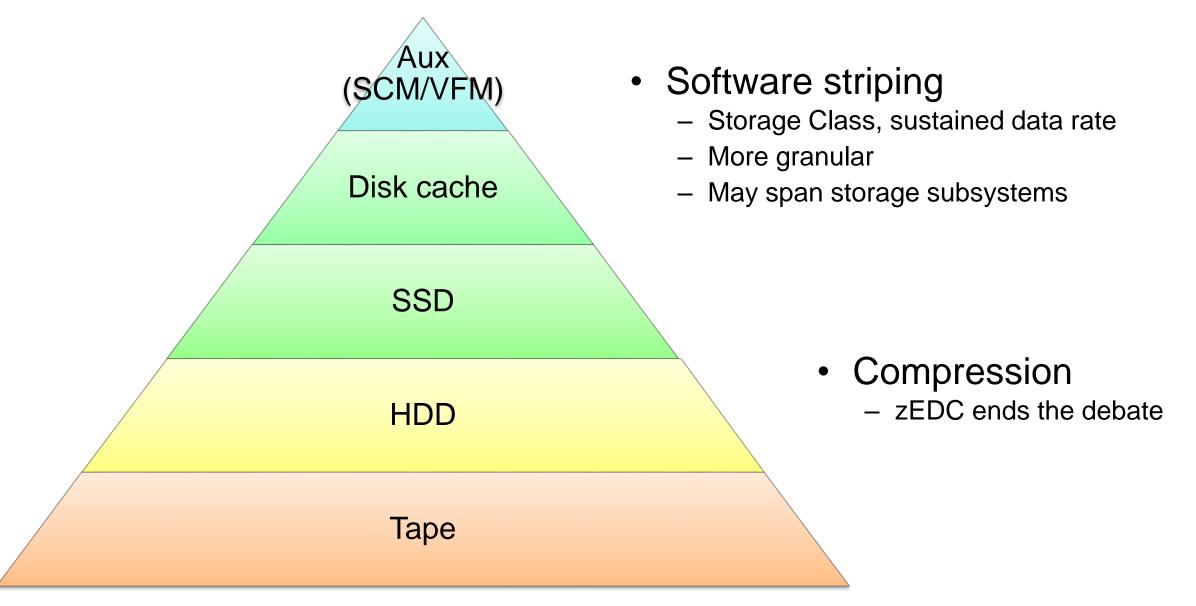

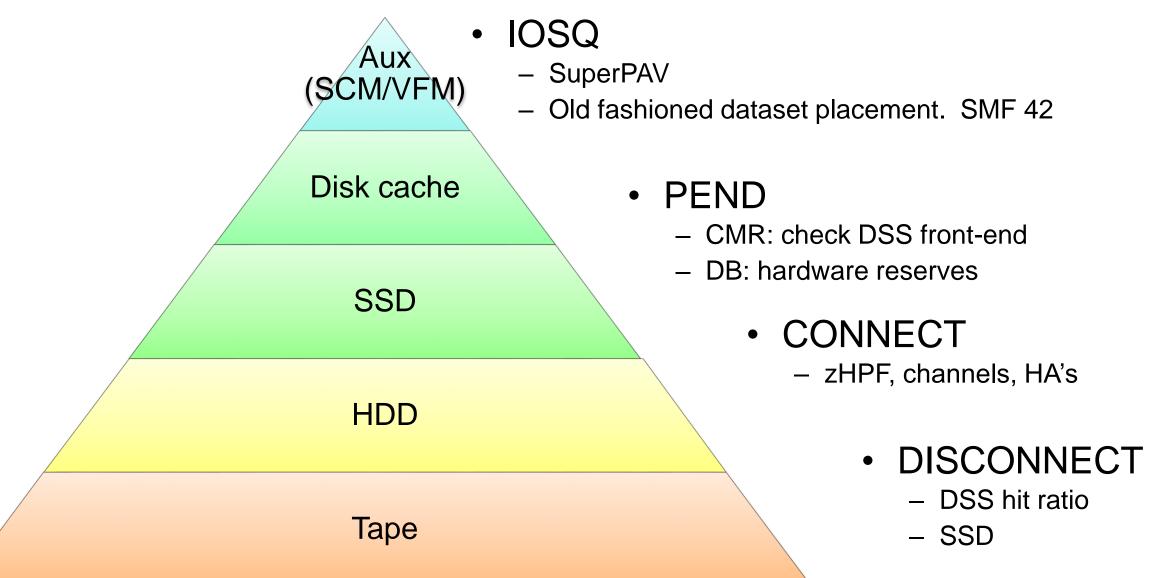

## **Storage Tiers**

8

## **Caching Principles**

- Temporal locality: Data that is accessed once, will likely be accessed again

- Try to hold data in cache as long as possible (LRU)

- Larger caches can hold more

- Spatial locality: Data near the same location as target data will likely be accessed as well

- Cache lines and sequential prefetch

- CPU performance goal: Must be able to access L1 cache in a single clock cycle

- L1 cache should not be too large to prevent this

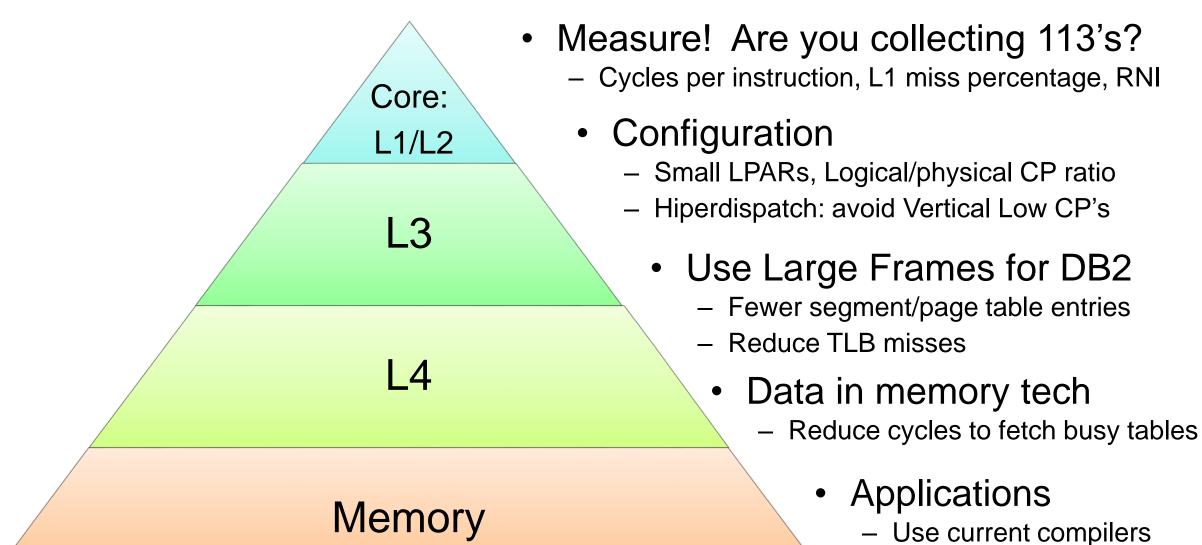

#### **Improving Sync Access**

Check your old assembler

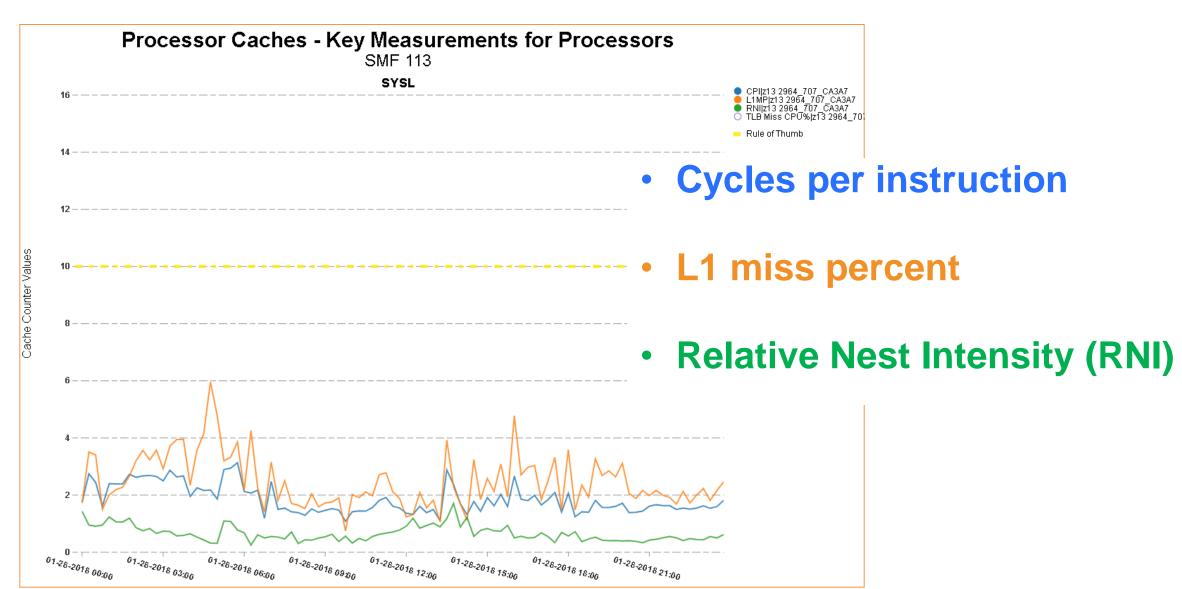

#### **Processor Cache Measurements**

#### **Improving Sync Access**

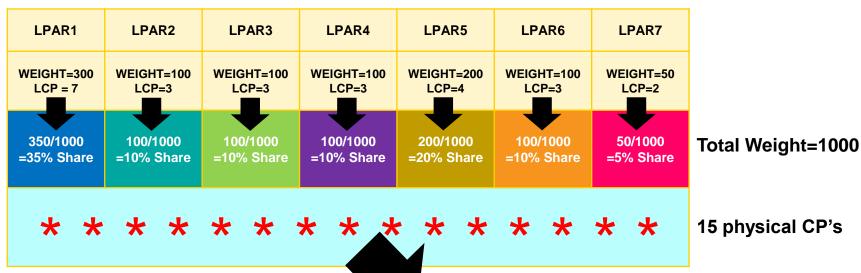

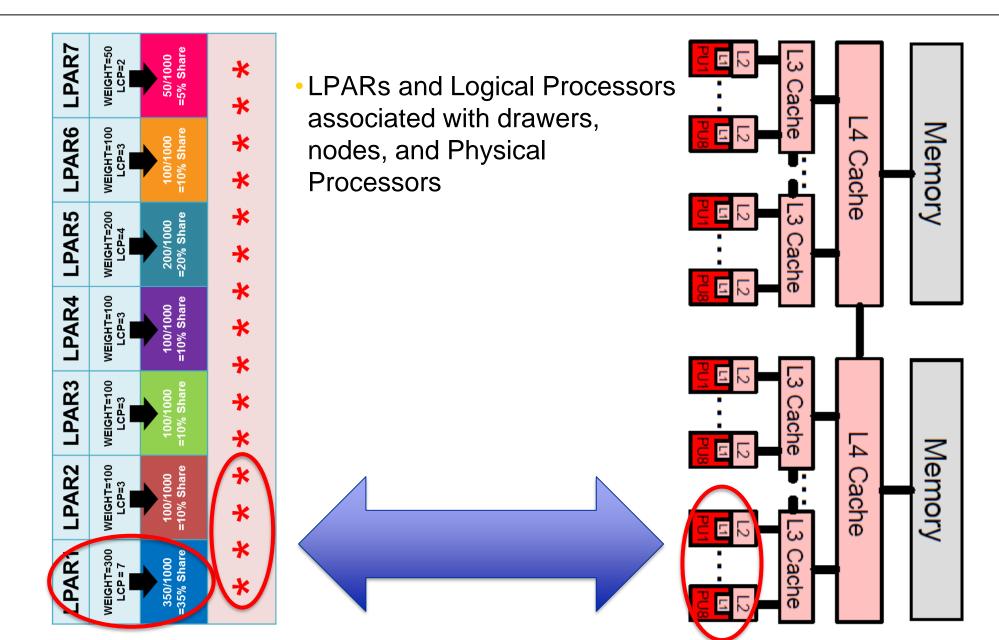

#### Pre-Hiperdispatch: "Horizontal" alignment

- Weight is guaranteed minimum

- May be exceeded if other LPARs do not use their full share

- Subject to number of LCPs (also limits maximum)

#### **HiperDispatch**

- A method of "aligning" physical CPUs with LPARs

- Goal is to take advantage of newer hardware design

- Also reduce multiprocessing overhead ("MP Effect")

- Default as of z/OS 1.13

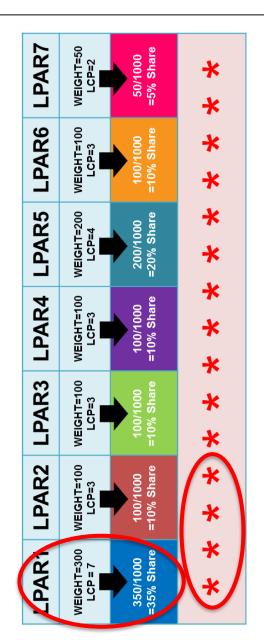

| HIPERDISPATCH = NO                                     | HIPERDISPATCH = YES                                        |

|--------------------------------------------------------|------------------------------------------------------------|

| "Horizontal" alignment                                 | "Vertical" alignment                                       |

| % share distributed across all available physical CPUs | % share distributed by physical CP                         |

| All CPs distributed among all LPARs                    | LCPs become "Vertical High, Vertical Medium, Vertical Low" |

| Utilization of all CP's tends to be even               | Unused (Vertical Low) CPs are "parked"                     |

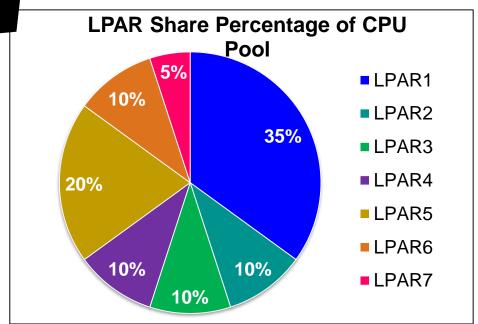

#### **Vertical Alignment**

- •LPAR1 example:

- 35% share, 7 LCP's = .35 \* 15 CP (Cores) = **5.25 CPs**

- 1.0 = VH, .5 .99 = VM, <.49 = VL \*\*\*

- First every LPAR receives at least one VM = ".5 CPs"

- 5.25 .5 = 4.75

- 4.75 4 (FOUR "whole CPs" = VH) = .75

- .75 .5 = .25 (one more VM)

- .25 (less than .5) = VL

- •= 4 \* VH, 2\* YM, 1\* VL

#### **PR/SM** Association

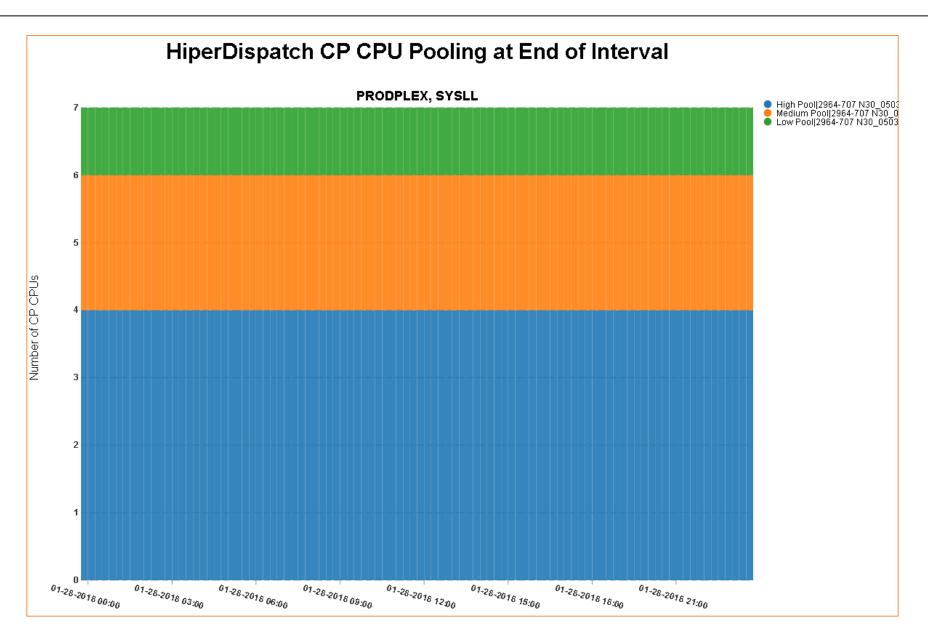

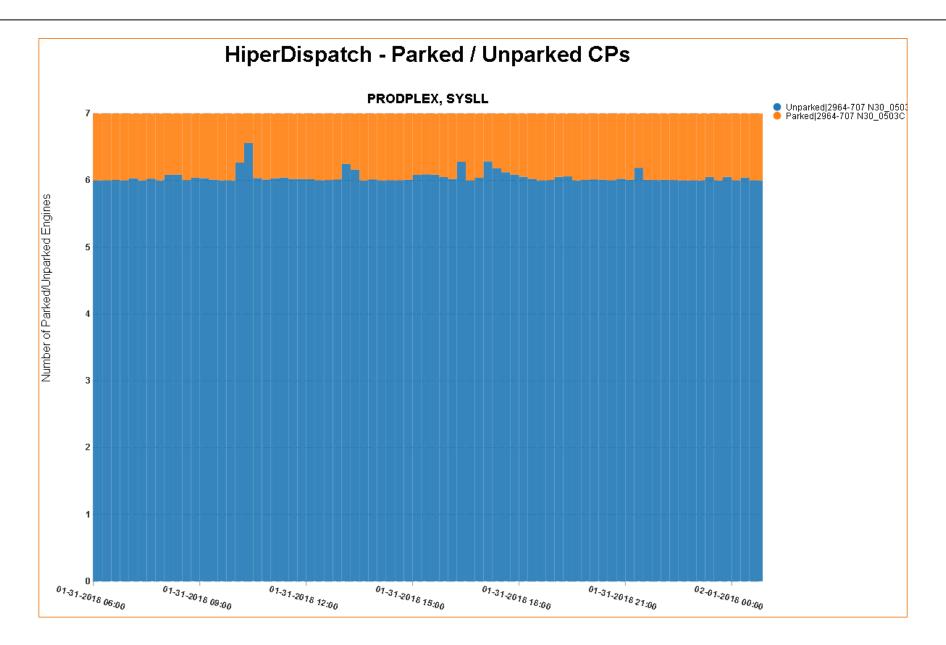

## **Hiperdispatch Config**

#### **Parked Processors**

## **Improving Sync Access**

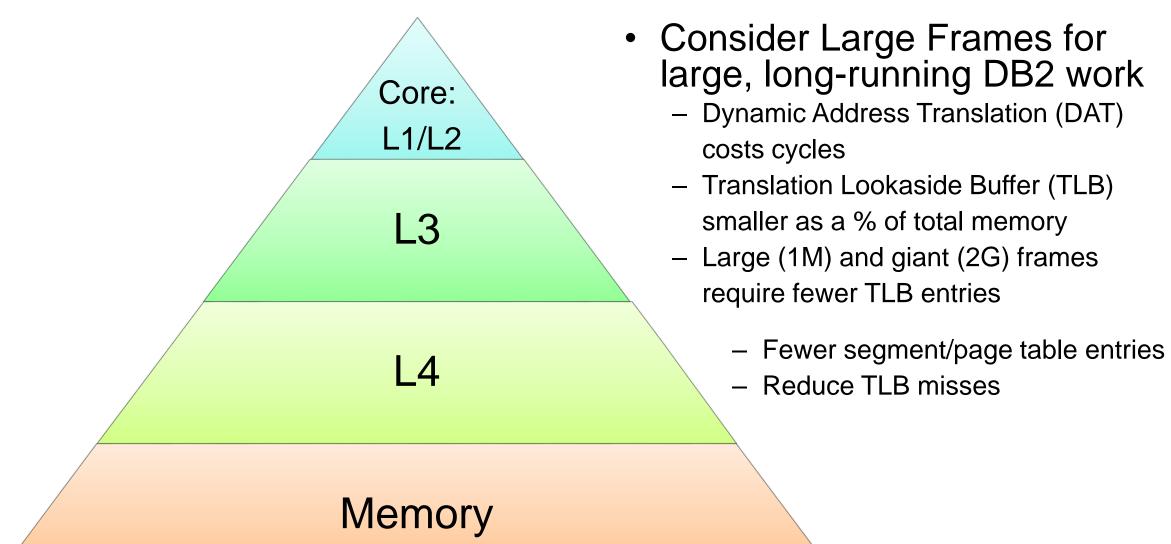

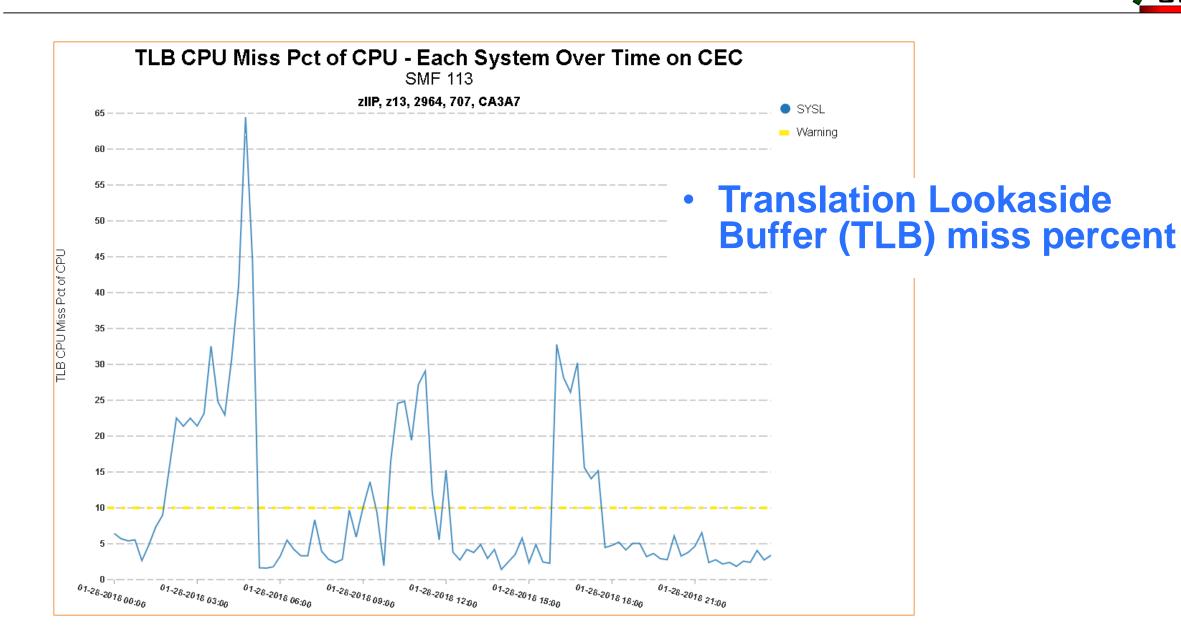

#### **DAT Cost**

#### **Improving Sync Access**

#### **Improving Async Access**

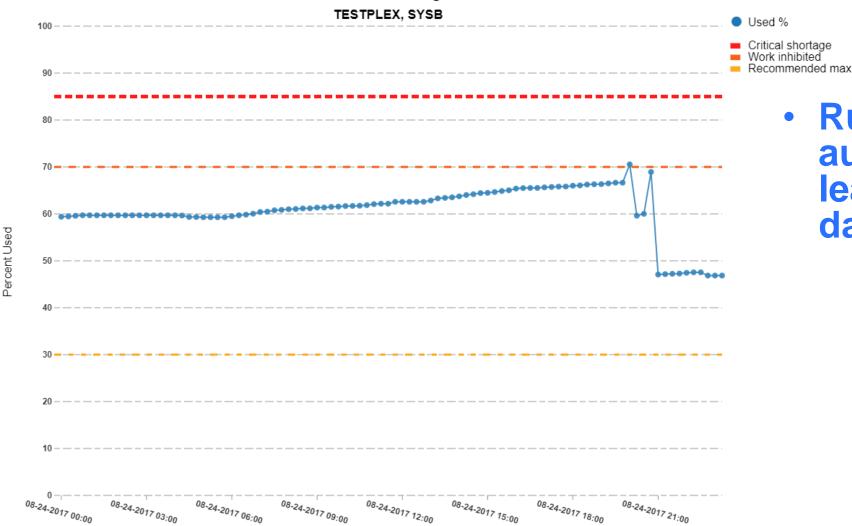

## **Aux Storage Use**

#### **Auxiliary Storage Utilization**

Interval Average

Running out of auxiliary storage can lead to a very bad day...

#### **Improving Async Access**

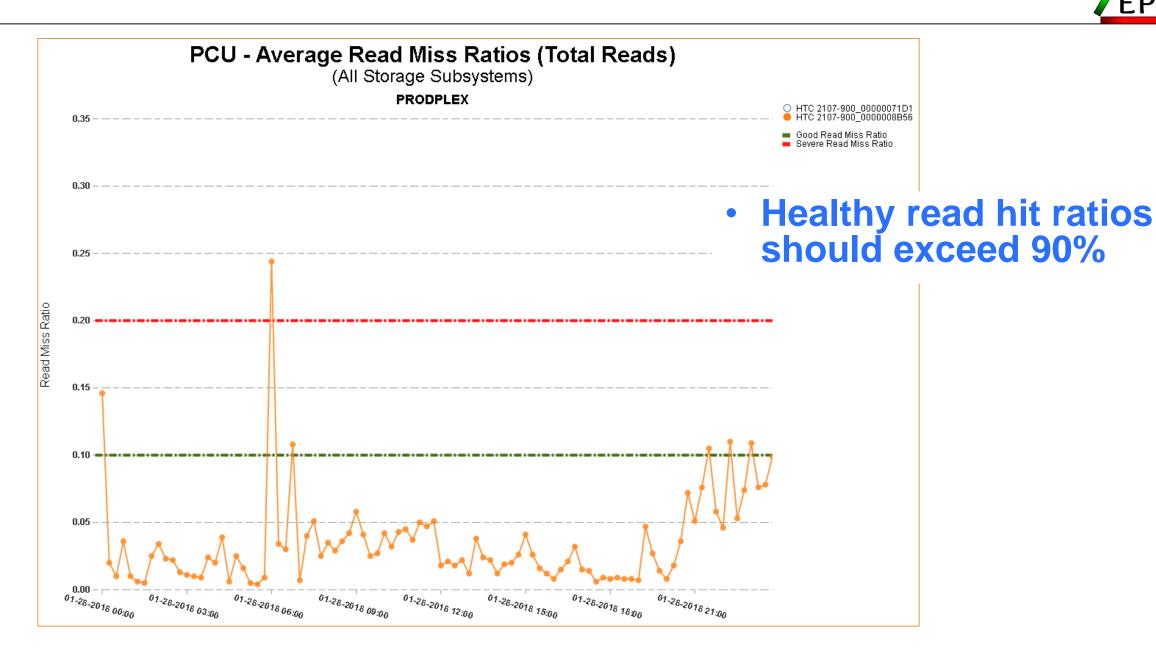

#### **DSS Cache Read Miss %**

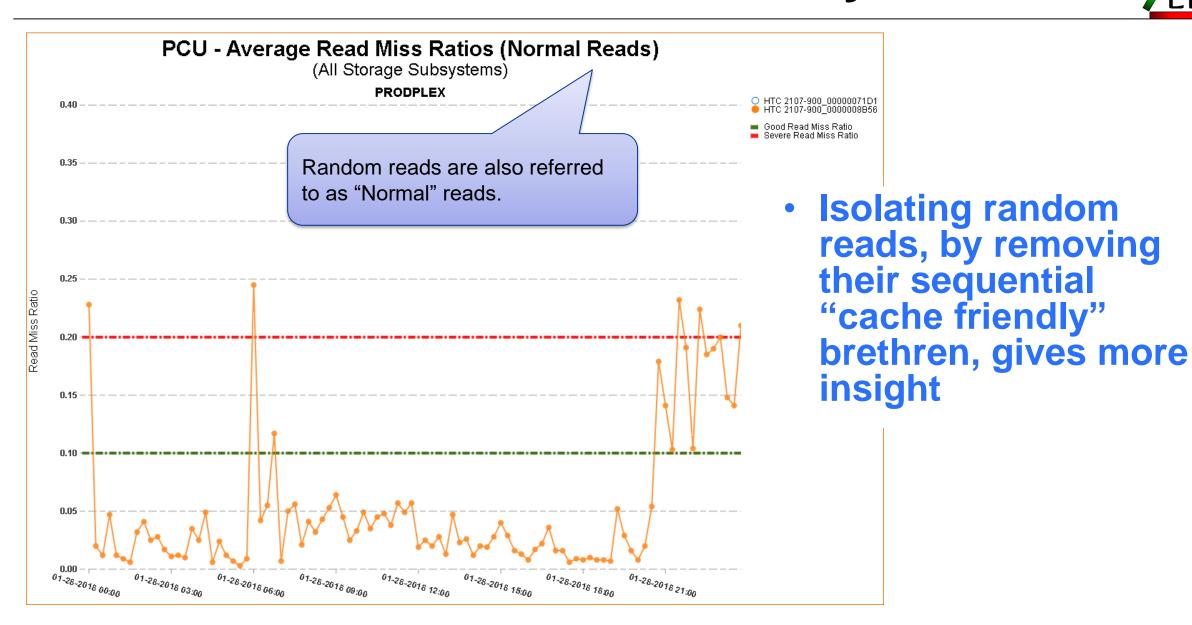

#### Random Reads only

#### **Improving Async Access**

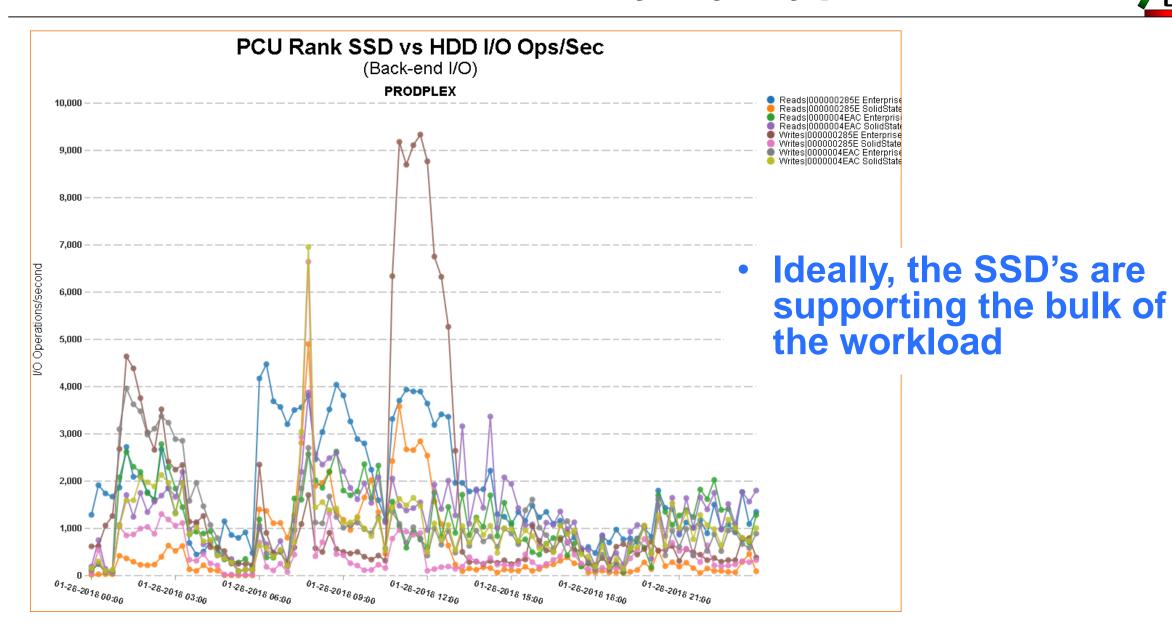

#### **Disk Activity by Type**

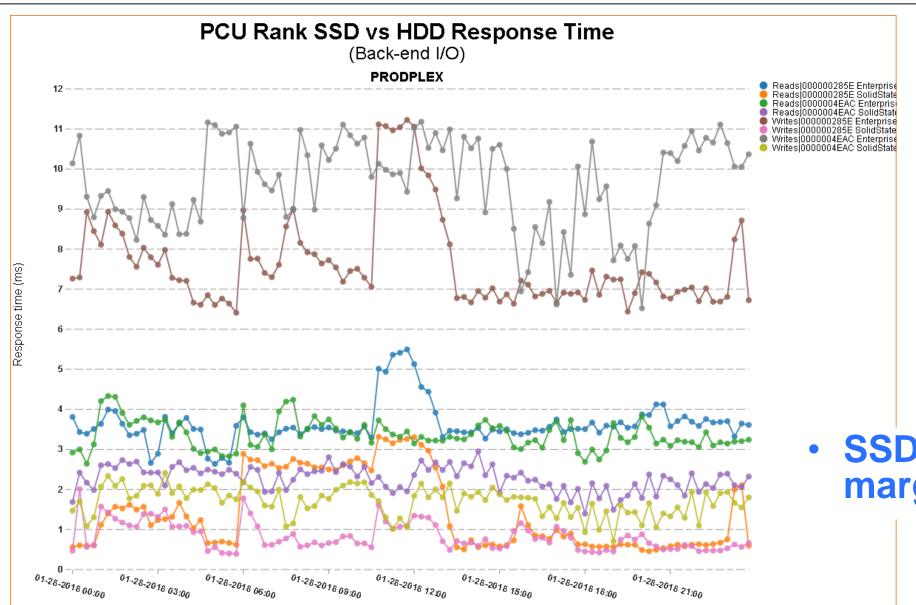

## Response by Disk Type

SSD benefit is marginal here

#### **Improving Async Access**

## **Improving Async Access (2)**

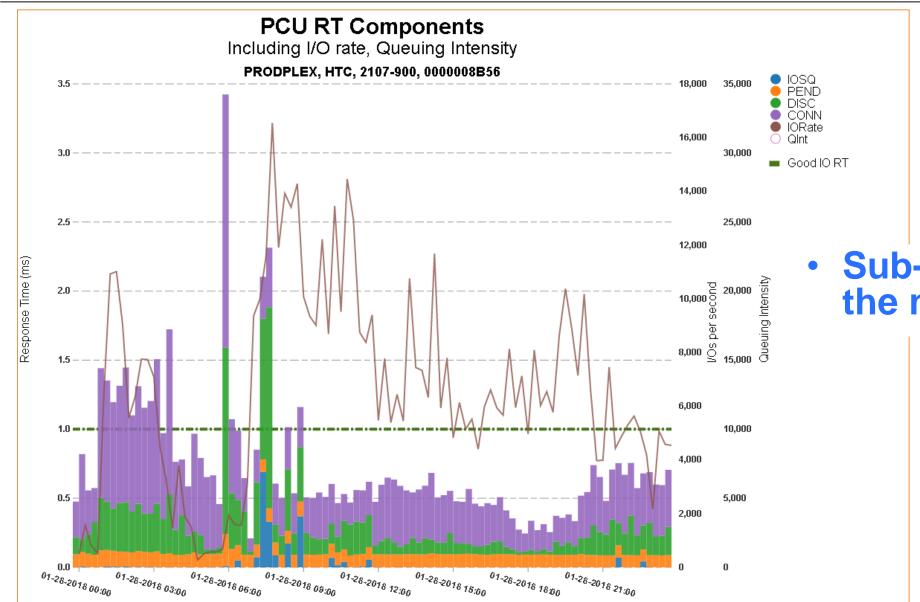

#### **Response Time Components**

Sub-millisecond is the new standard

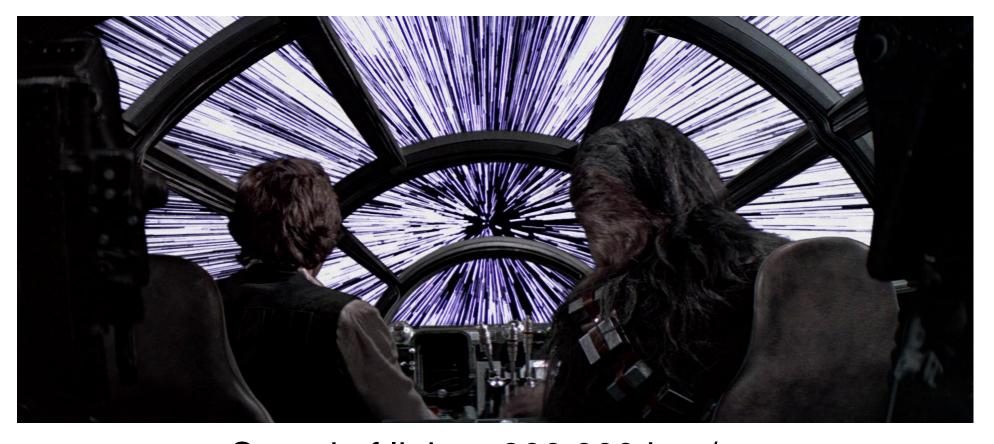

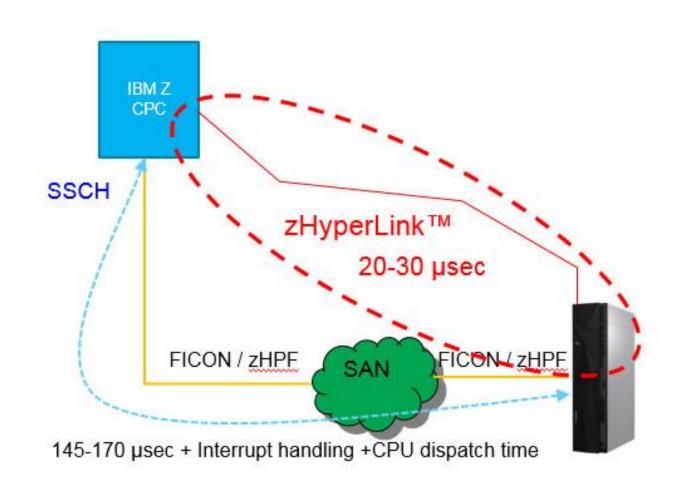

#### Something new: zHyperLink

#### zHyperlink Requirements

- Z14

- z/OS 2.1

- DS888x with zHyperlink feature (FC #0431)

- DB2 v11+ only (for now)

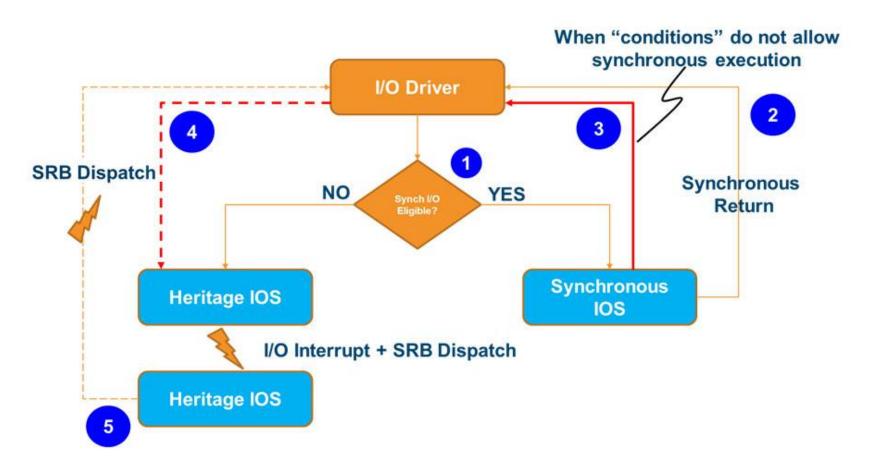

#### zHyperlink Flow

- Conditions

- Why not make everything sync?

http://www.redbooks.ibm.com/Redbooks.nsf/RedpieceAbstracts/redp5186.html?Open

## "External memory"

# Thank you!